(System Python)

In this SoC design we wanted to demonstrate how SysPy can be used to describe custom

hardware blocks for audio processing, connected to a programmable processor core running

software on top of a Linux kernel, for controlling the SoC and exchanging data over an Ethernet

network with a connected host PC. A top level schematic of the system can be found in the figure below.

The Leon3 processor core is connected to four, 30-taps, FIR filters, which are used to extract

the frequency content of music files, processed in wav format files. The music files are

transfered to the processor in the FPGA board via Ethernet connection. An FTP client is running

in the processor, on the Linix kernel, transfering the files from an FTP server running on the

connected host PC. An interface unit/state machine is used to control the data flow between the processor

and the filter bank. Two 64kx32-bit FIFO memories, implemented using the Xilinx IP core generator, are used

as data buffers between the two different clocking domains of the processor (160MHz) and the filter bank

(90MHz).

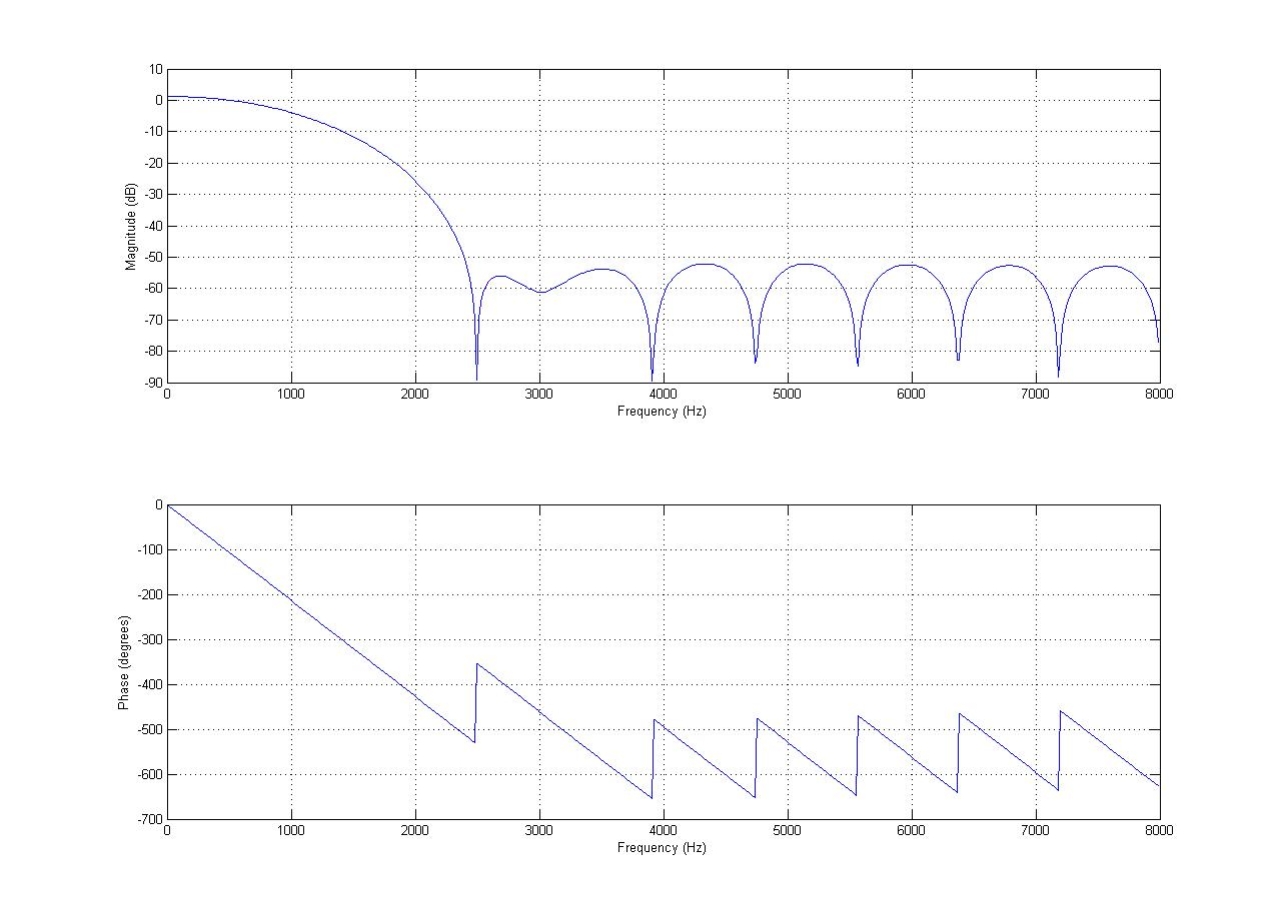

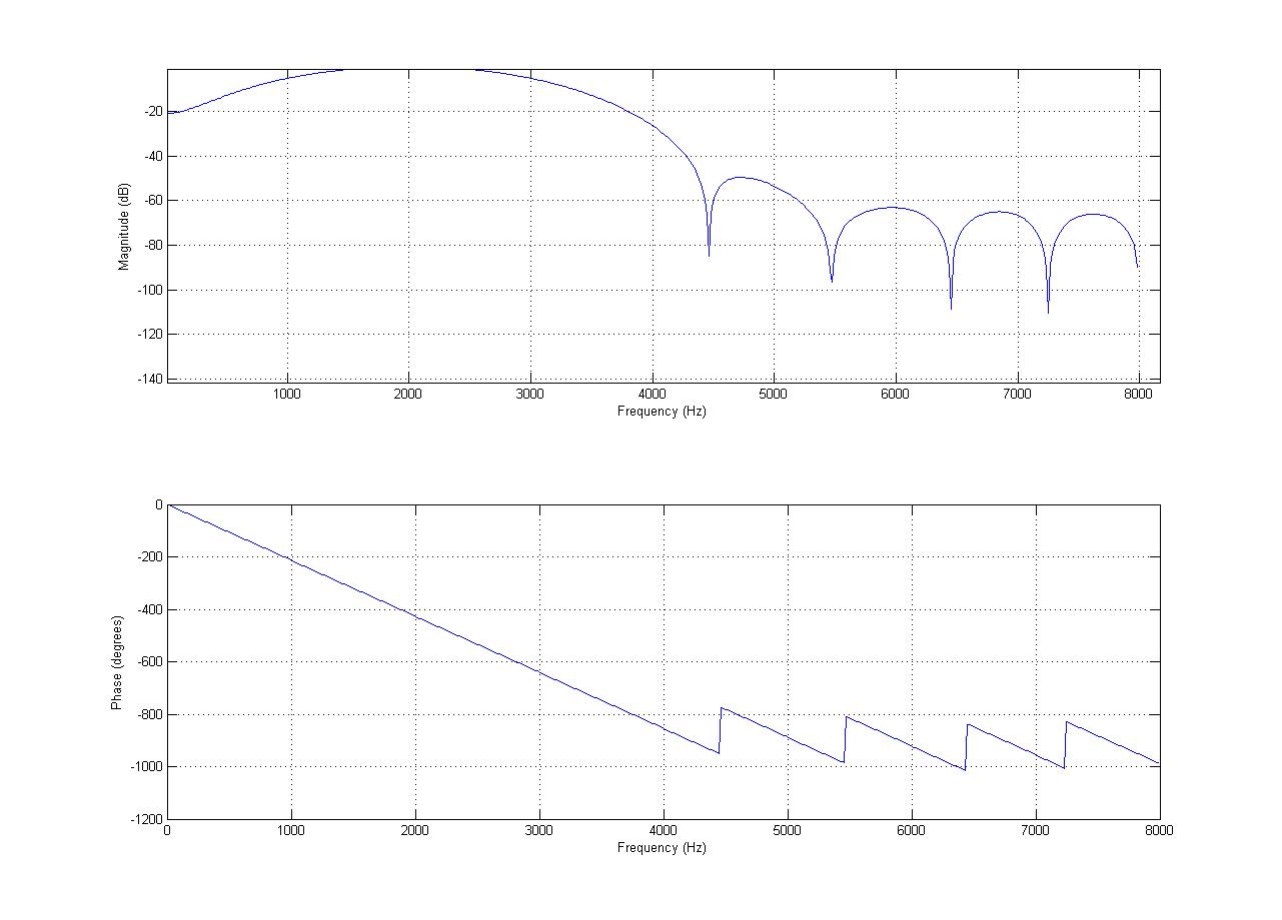

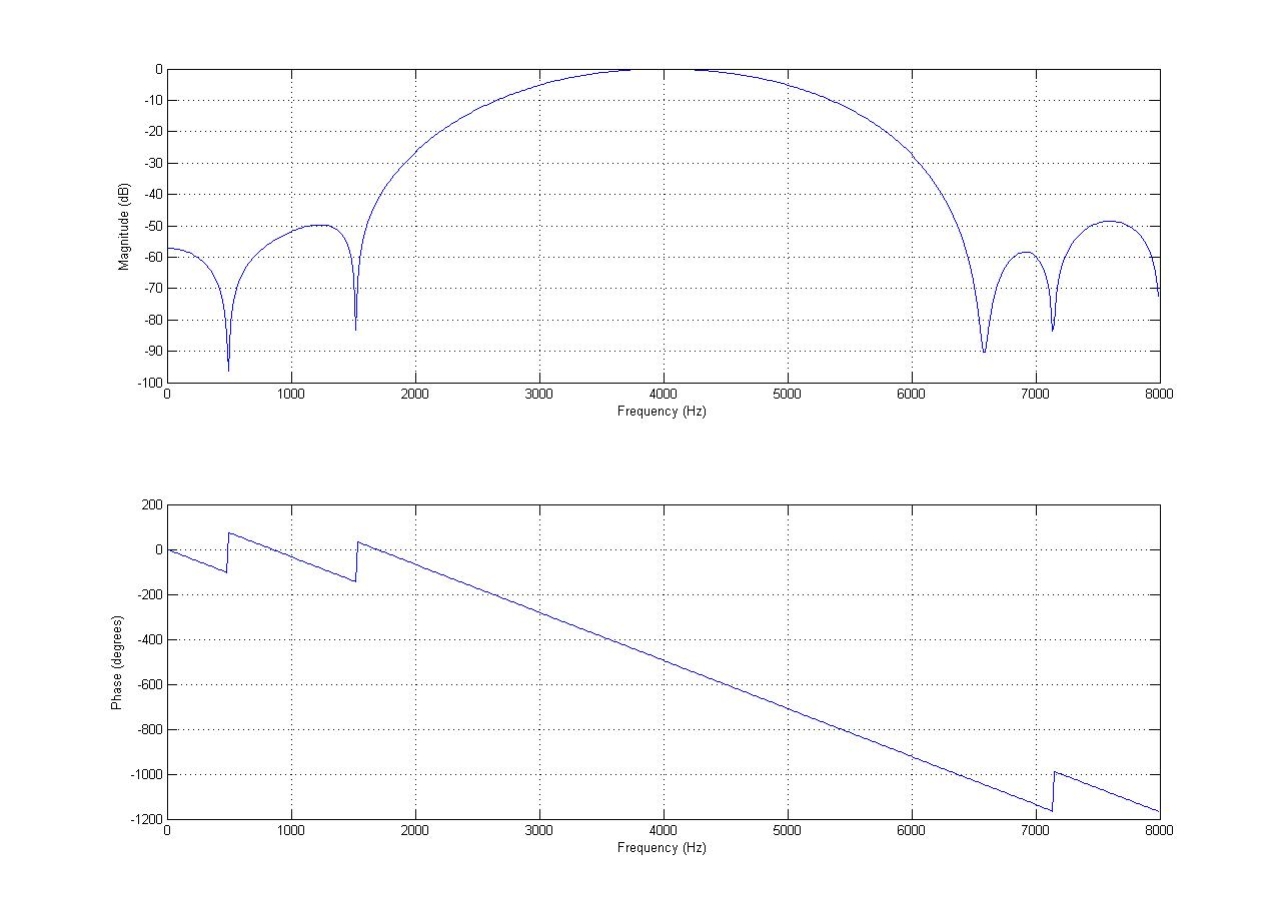

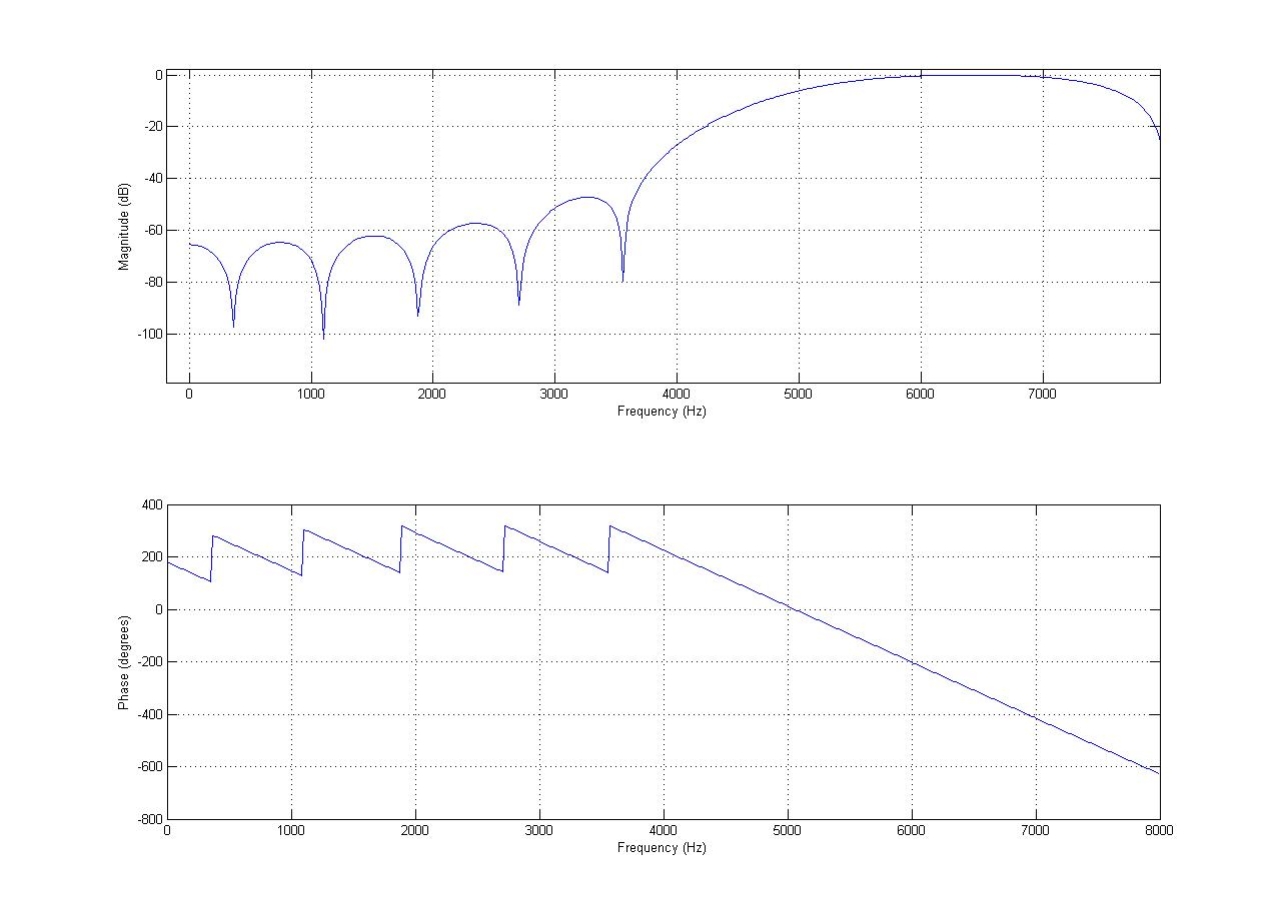

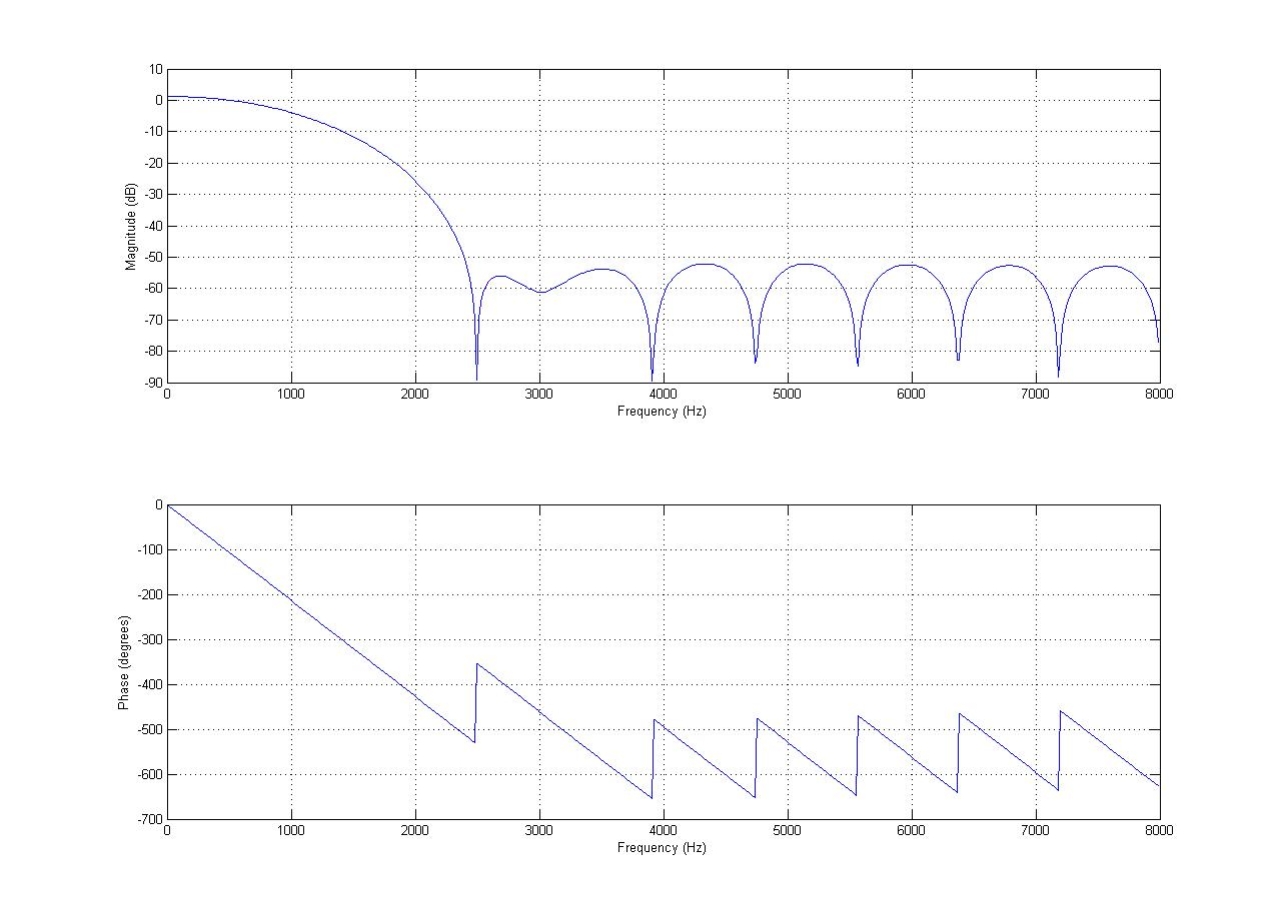

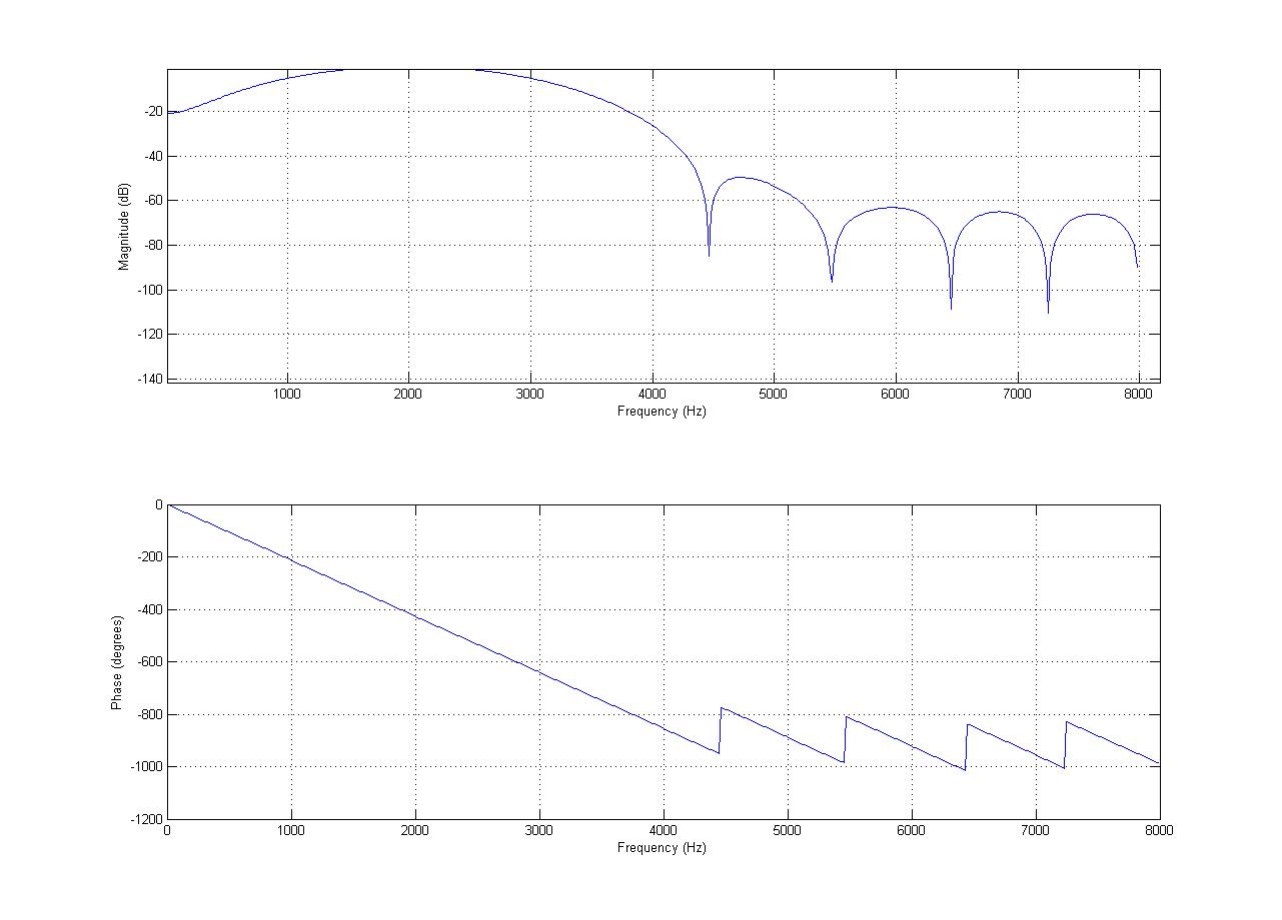

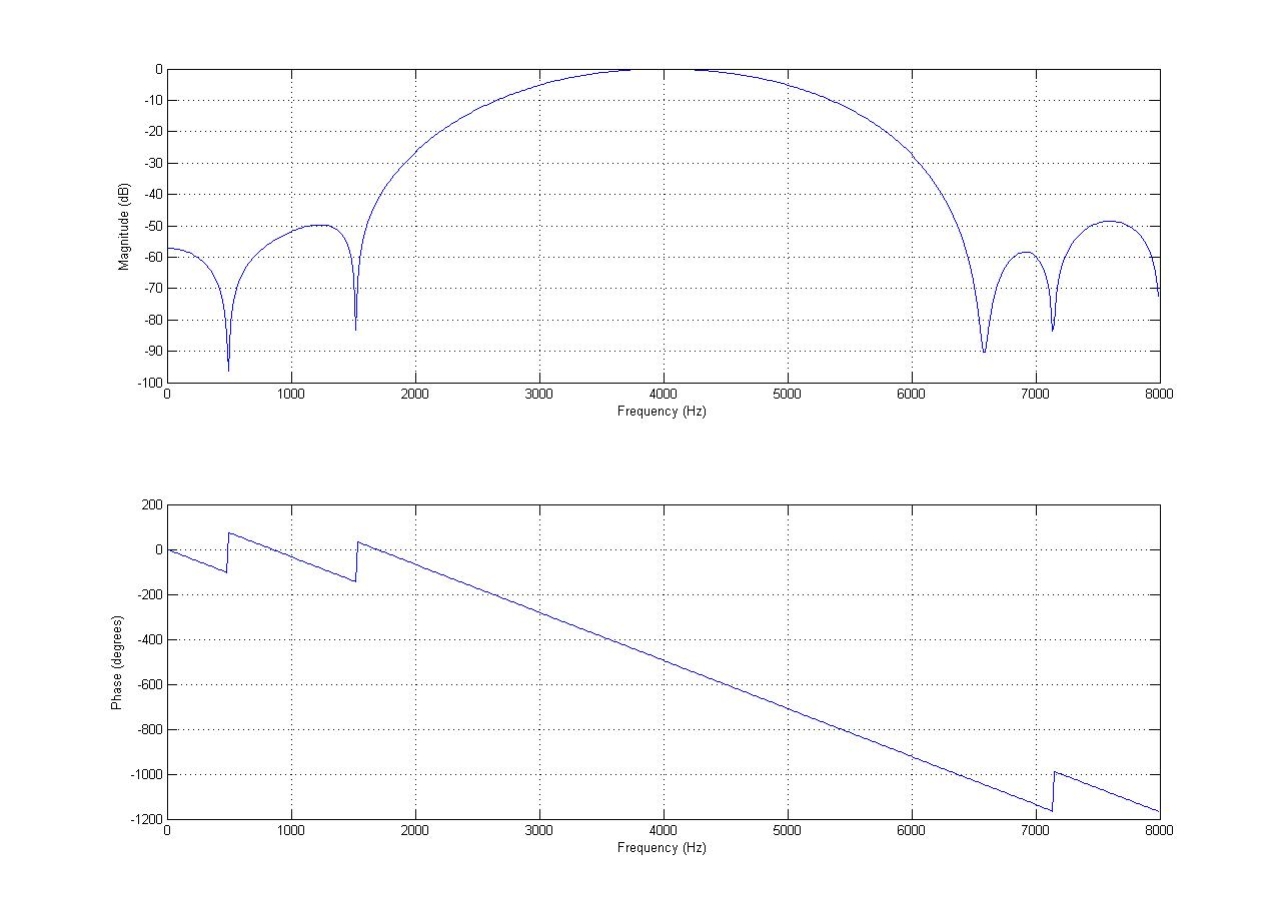

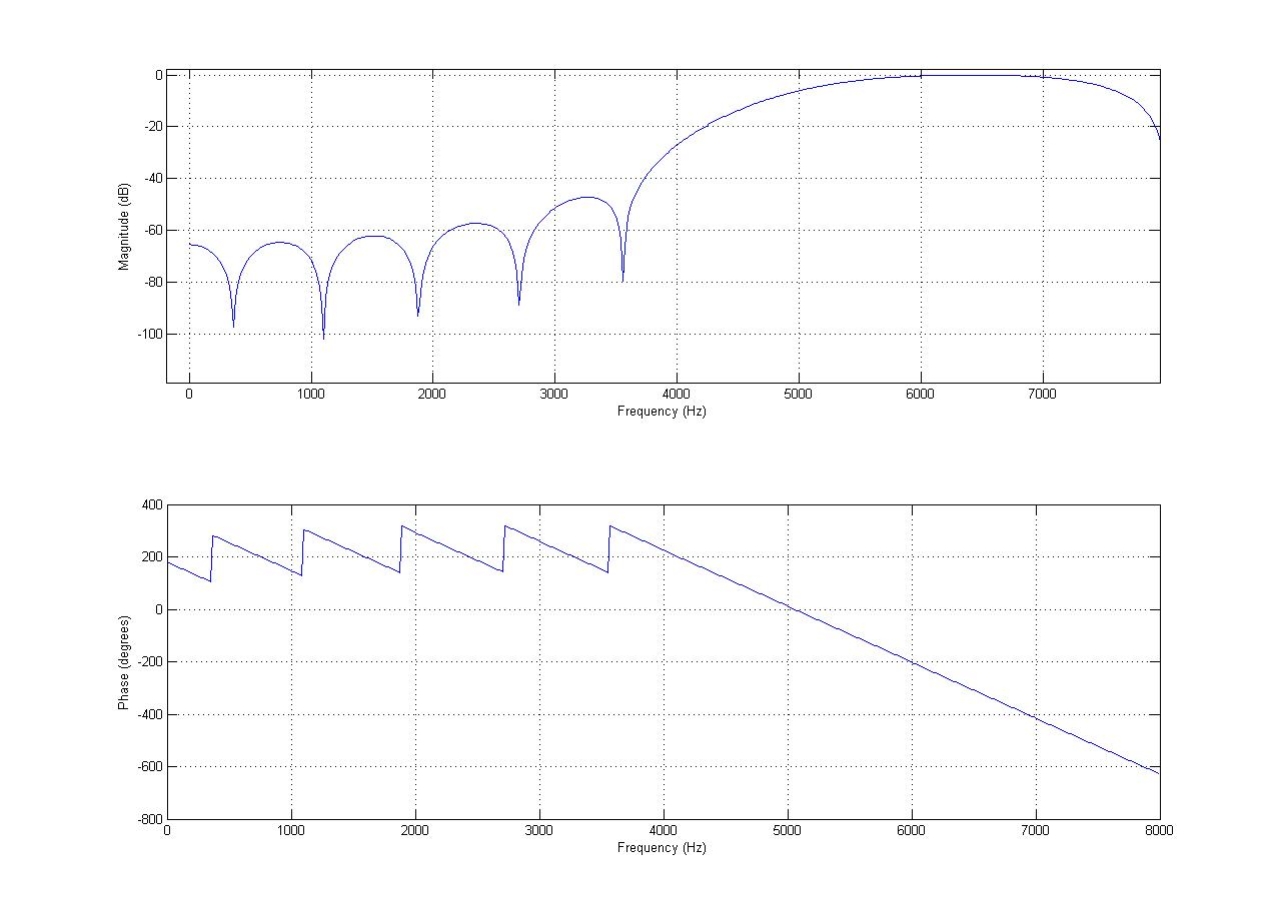

The four filters divide the audible spectrum of the music files into four regions. According to

the frequency content, every file is classified to one of four music styles (rock, pop, classical,

electro). The four designed filters had 30-tap each and their coefficients have been calculated

using SciPy (0-1KHz, 1-3KHz, 3-5KHz, 5-8KHz). The impulse response

plots for each filter can be found below.

[0 - 1kHz]

[1 - 3kHz]

[3 - 5kHz]

[5 - 8kHz]

All the top-level Python files describing the audio processing SoC, as well as

the generated VHDL files and the Tcl script used for the FPGA implemenetation in a Xilinx

Virtex-5 device, can be found below:

Python - VHDL descriptions

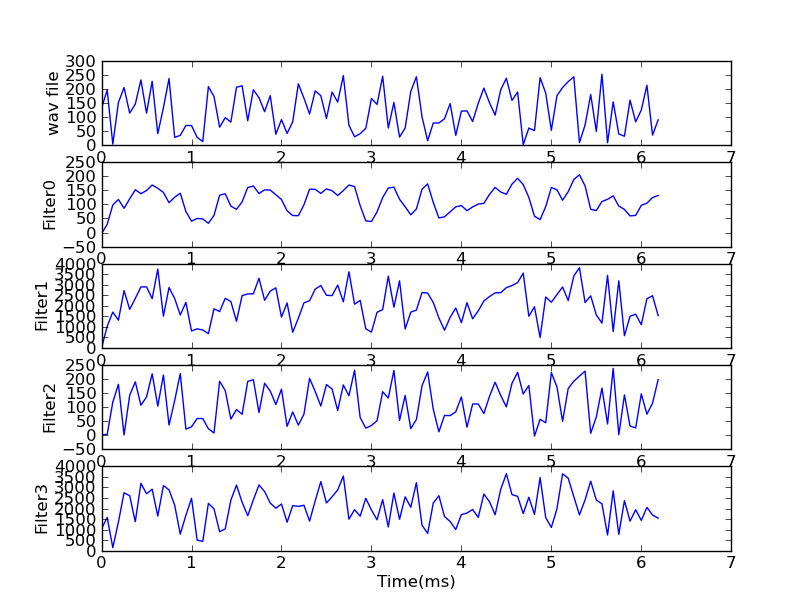

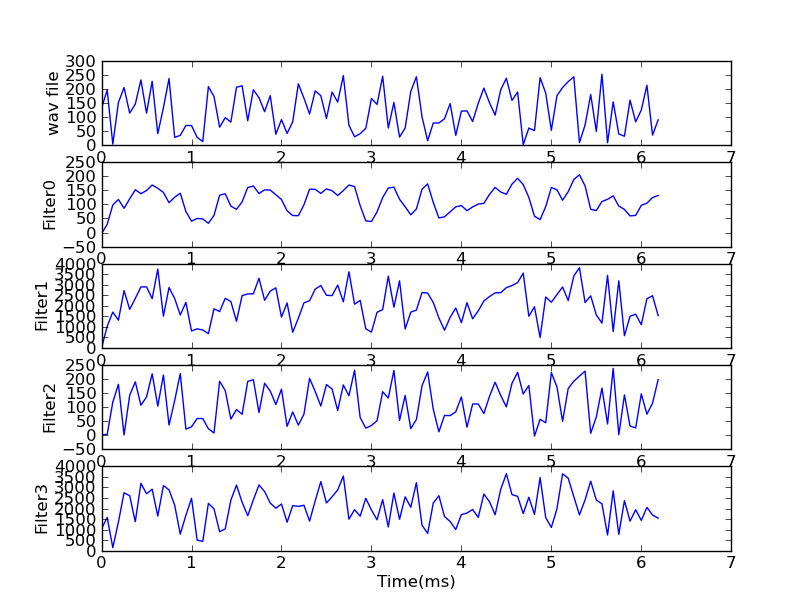

Except describing a SoC on the Python level, wwe also wanted to be able to verify/co-simulate the

Python RTL descriptions and parts of the sofware running in the processor core and decide about

key fetuares of a design early in the design phase. Using Python's object oriented features we are able to

simulate a) the control software running on the processor and also b) the behavior of RTL blocks not yet described

using an HDL. Functions and classes in SciPy's libraries can also be used to

describe algorithmic behavior and arithmetic operations that will be later implemented in software or hardware. Plots

of processed signals in Scipy during simulation can also be generated during simulation, using fixed-point or

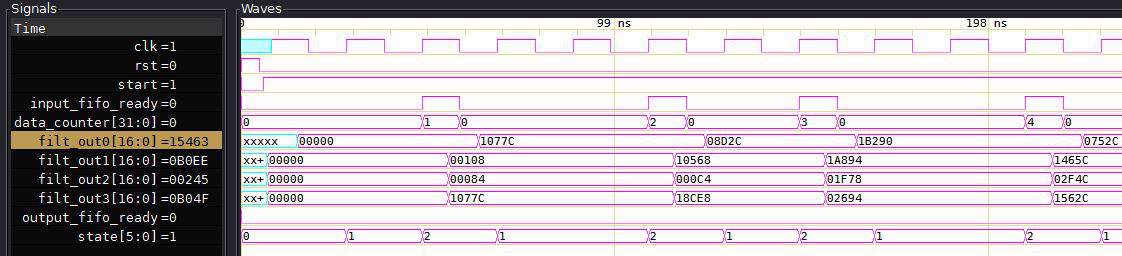

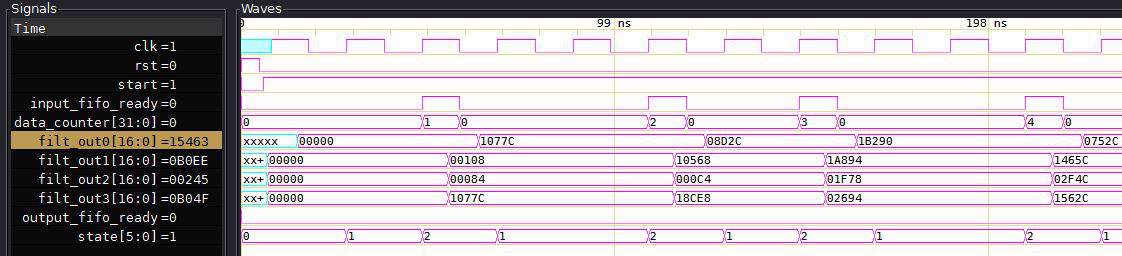

floating-point arithmetics. The behavior of I/O digital signals is captured using Value Change Dump (VCD) format.

The generated VCD files can be visualized using popular simulation tools, like

GTKWave and ModelSim.

Examples of signals' waveforms in SciPy and GTKWave (using the VCD generated file) during simulation runs, using SysPy,

are presented in the figures below.

(Plots of the music files samples and of the filtered signals in the output of the four filters)

(Waveforms of audio SoC's I/O signals, using GTKWave.)

The simulation files, using Python code, used to simulate the pipelined datapath of the four filters, along with the auto-generated

IP-XACT (xml) model of the top-level simulation file and also the software running in the processor and generate the signal plots in SciPy

and the VCD files with the digital waveforms of all the I/O signals, can be found in the following link:

Python - simulation models

Main Page